- 您现在的位置:买卖IC网 > Sheet目录39245 > LM12H458MWG-MCP (NATIONAL SEMICONDUCTOR CORP) SPECIALTY ANALOG CIRCUIT, CDFP44

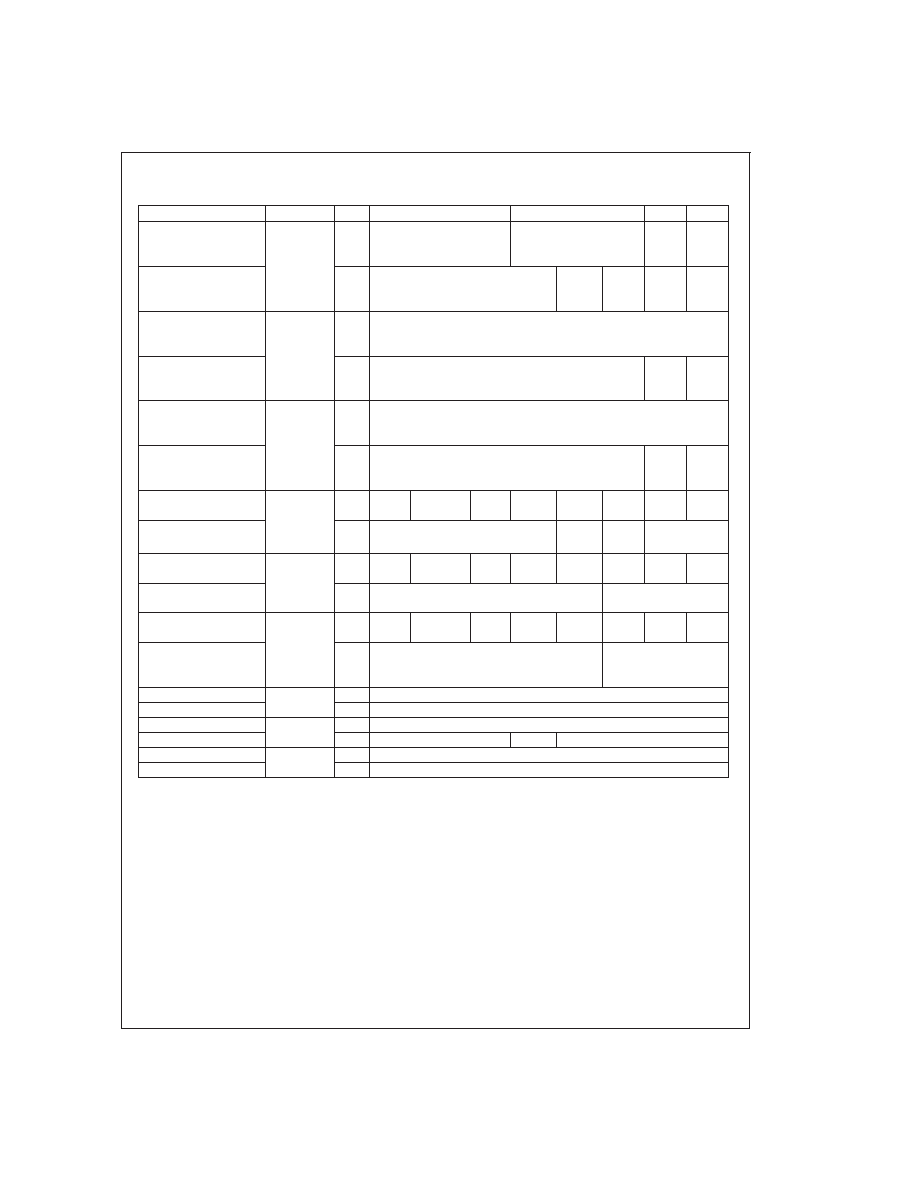

2.0 Internal User-Programmable Registers (Continued)

Note 22: LM12454 (Refer to

Table 2).

Note 23: LM12(H)458 only. Must be set to “0” for the LM12454.

A4

A3

A2

A1

A0

Purpose

Type

D7

D6

D5

D4

D3

D2

D1

D0

000

Instruction

RAM

(RAM

Pointer =

00)

R/W

VIN

(MUXOUT) (Note 22)

VIN+

(MUXOUT+) (Note 22)

0to0

Pause

Loop

111

0

R/W

Watch-

0

to

1

Acquisition Time

dog

8/12

Timer

Sync

111

000

Instruction

RAM

(RAM

Pointer =

01)

R/W

0

to

0

Comparison Limit #1

111

000

R/W

0

to

1

Don’t Care

>/<

Sign

111

000

Instruction

RAM

(RAM

Pointer =

10)

R/W

0

to

0

Comparison Limit #2

111

000

R/W

0

to

1

Don’t Care

>/<

Sign

111

10000

Configuration

Register

R/W

I/O

Auto

Chan

Stand-

Full

Auto-

Reset

Start

Sel

Zeroec

Mask

by

Cal

Zero

10001

R/W

Don’t Care

DIAG

(Note

23)

Test =

0

RAM Pointer

10010

Interrupt

Enable

Register

R/W

INT7

INT6

INT5

INT4

INT3

INT2

INT1

INT0

10011

R/W

Number of Conversions in Conversion

Sequencer Address to

FIFO to Generate INT2

Generate INT1

10100

Interrupt

Status

Register

R

INST7

INST6

INST5

INST4

INST3

INST2

INST1

INST0

10101

R

Actual Number of Conversions Results

Address of Sequencer

in Conversion FIFO

Instruction

being Executed

10110

Timer

Register

R/W

Timer Preset: Low Byte

10111

R/W

Timer Preset: High Byte

11000

Conversion

FIFO

R

Conversion Data: LSBs

11001

R

Address or Sign

Sign

Conversion Data: MSBs

11010

Limit Status

Register

R

Limit #1 Status

11011

R

Limit #2 Status

FIGURE 14. LM12(H)454/8 Memory Map for 8-Bit Wide Databus (BW = “1” and Test Bit = “0”)

www.national.com

25

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LM12H458MWG/883

SPECIALTY ANALOG CIRCUIT, CDFP44

LM1262NA/NOPB

3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24

LM129BH/883

1-OUTPUT TWO TERM VOLTAGE REFERENCE, 6.9 V, MBCY2

LM129BH

1-OUTPUT TWO TERM VOLTAGE REFERENCE, 6.9 V, MBCY2

LM12H454CIV

SPECIALTY ANALOG CIRCUIT, PQCC44

5962-9319501MXC

SPECIALTY ANALOG CIRCUIT

5962-9319502MYX

SPECIALTY ANALOG CIRCUIT, PQCC44

5962-9319501MYX

SPECIALTY ANALOG CIRCUIT, PQCC44

相关代理商/技术参数

LM12L438CIV

制造商:NSC 制造商全称:National Semiconductor 功能描述:Sign Data Acquisition System with Serial I/O and Self-Calibration

LM12L438CIWM

制造商:NSC 制造商全称:National Semiconductor 功能描述:Sign Data Acquisition System with Serial I/O and Self-Calibration

LM12L454CIV

制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述:

LM12L458

制造商:NSC 制造商全称:National Semiconductor 功能描述:12-Bit + Sign Data Acquisition System with Self-Calibration

LM12L458_06

制造商:NSC 制造商全称:National Semiconductor 功能描述:12-Bit + Sign Data Acquisition System with Self-Calibration

LM12L458CIV

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

LM12L458CIV/NOPB

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

LM12L458CIVF

制造商:Rochester Electronics LLC 功能描述:12-BIT PARALLEL I/O DAS - Bulk